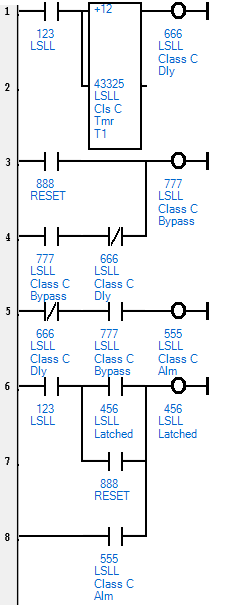

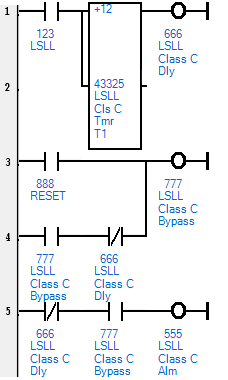

The purpose of this article is to provide an educational reference for logic pertaining to Class Shutdown (SD). See snippet below.

In a nutshell, when the Modbus register 123 (“LSLL”) enters alarm state (de-energizez) the timer Modbus Register 43325 is reset to zero (ready to count up). When the Modbus register 123 (“LSLL”) returns to normal (energizes), the Modbus register 456 (LSLL latch) is kept energized via Modbus Register 555 (LSLL Class C Alm) until the timer Modbus Register 43325 expires in 12 seconds. This will prevent the process to going in alarm or SD state again when the LSLL de-energizes before the 12 seconds timer expires.

Alarm latching logic (rung 1 to 5). Note that you have to energize the Modbus register 888 (RESET) when the LSLL is de-energize to arm the Class C logic.

IO alarming logic (rung 6 to 8). Note the Modbus Register 555 (LSLL Class C Alm)